嵌入式设计常被忽略的硬件常识

在实际示波器采样来看,就表现在上电初期IO脚会有一个短暂(当时是持续大约几百us)的高脉冲。虽然当时遇到的一些闪屏现象在外接一个10K下拉电阻后得到解决,但是近期特权同学又遇上换汤不换药的类似问题。有了前车之鉴,问题定位很快。用示波器一采样,怪哉,在上电初期居然有1。68V左右的高脉冲,和上回唯一的不同是器件更换了,之前是MAX II家族,而这次是Cyclone III家族。那么他们在上电弱上拉的一些细节上又有怎样的不同呢。

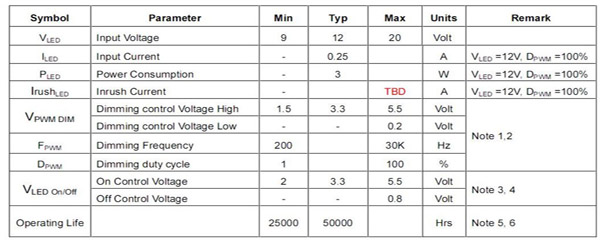

在同样的FPGA外部输出IO脚下拉了10K的电阻,用示波器采样到上电初期也确实有一个瞬间的高脉冲,这个高脉冲维持了200ms左右,而且电压值居然高达1。68V,IO的电平是标准的LVTTL,高电平3。3V,那么1。68V差不多是减半的样子。由此推断,此时IO脚上的弱上拉好像不弱,应该也在10K左右。推想归推想,特权同学将外部下拉的10K换成了4。7K,再一测试,闪屏现象虽然有所好转,但还是没有完全根除,抓取到上电初期的高脉冲大约在1V多点。从理论上想,1V肯定不会被认为是TTL的高电平,但是为什么依然出现了高电平而使能背光的一个状况呢?翻看datasheet,在图1所示的VLED on/off一行的高低电压参数中,2V~5。5V被认为是高电平开启背光,而低于0。8V被认为是低电平关闭背光。那么处于0。8V~2V之间的两不管地带电平到底又会被认为是开还是关背光呢?实践告诉我们至少1V时是开背光了(当然也许长期的1V电压不会得到稳定的背光开启状态)。所以,再降低外接下拉电阻才可能解决问题。

图1

于是换成了2K的下拉,和预想的一样,此时的上电高脉冲在0。55V左右(满足Off Controller Voltage电压),完全印证了IO管脚内部上拉10K电阻的初步推断。关于上电弱上拉,其实特权同学也想到了JTAG的TCK/TMS/TDI上拉或下拉都用1K电阻也许与此也有一定的关系。此外,在Quartus II的管脚约束中有Weak Pull-Up Resistor一项,原本天真的以为这个选项可以更改IO管脚上电时的弱上拉开启与否,但是实践证明不是这样,至于具体的用法和功能,特权同学也没有在Handbook中找到,或许这个选项是用于设置IO正常工作期间内部是否进行弱上拉。

其实特权同学在这里不是要再次强调这个所谓的上电弱上拉,而是想提一下数字电路中的电平标准。也就如标题所示,被忽略的硬件常识,至少特权同学近来或者说一直以来都不太关心这个问题。电平标准,最常见就是TTL和CMOS,他们的异同优劣用不着我费口舌,大家肯定比我清楚。而在前面遇到的问题当中比较有意思的就是1V这样即非高电平又非低电平的悬浮状态居然也被高电平了。

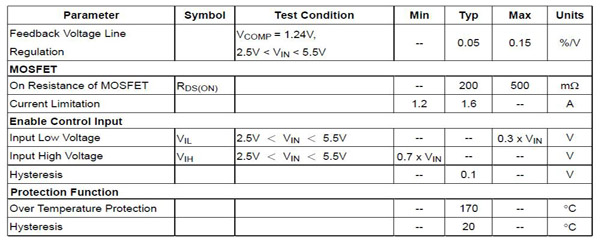

其实,特权同学还遇到了一个被疏忽的背光使能的问题,所以才需要发点感慨让自己清醒些。如图2所示,一颗升压芯片的电气特性截图,需要关心的是Enable Control Input一栏。

图2

在特权使用的这个升压电路中,VIN是5V,而使能信号想当然的用FPGA的3。3V TTL电平供过去了(之前有另一颗芯片按这个标准没有问题的),结果可想而知。出现的状况是无负载状态升压输出12V很稳定,一旦外接负载则输出跌落到仅有6V多,最终在图2的电气特性中才发现问题。被认为是High Voltage的最低电压应该是0。7*VIN,对于我的电路就是0。7*5V = 3。5V,而用FPGA的3。3V高电平供过去显然还没有达标,那么不稳定也就理所当然了。

其实,设计中我们有很多遗漏疏忽的考虑,究其根本原因也许不仅仅是我们看datasheet不够认真,不太细心。而是由于太多的先入为主的观念在影响着我们的思维,太多基本的硬件设计常识无形中被我们忽略了。我想,一个优秀的硬件工程师也许不是不犯错,而是转得快。